Product Summary

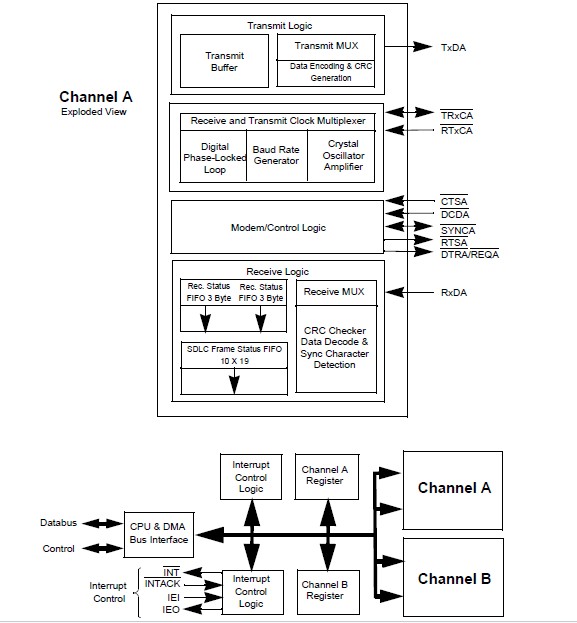

The Z85C3010VSC is a Serial Communications Controller (SCC). The Z85C3010VSC is a pin and software compatible CMOS member of the SCC family introduced by ZiLOG in 1981. It is a dual channel, multi-protocol data communications peripheral that easily inter­faces to CPUs with either multiplexed or non-multiplexed address/ data buses. The Z85C3010VSC process offers lower power con­sumption, higher performance, and superior noise immunity. The programming flexibility of the internal registers allows the SCC to be configured to satisfy a wide variety of serial communications applications. Figure 1 illustrates a block diagram of the SCC. The many on-chip features such as Baud Rate Generators (BRG), Digital Phase Locked Loops (DPLL), and crystal oscillators reduce the need for external logic. Additional features include a 10 x 19-bit status FIFO and 14-bit byte counter to support high speed SDLC transfers using DMA controllers.

Parametrics

Z85C3010VSC absolute maximum ratings: (1)Vcc Supply Voltage range: -0.3V to +7.0V; (2)Voltages on all pins with respect to GND: -3V to VCC +0.3V; (3)Ta Operating Ambient Temperature: See Ordering Information; (4)Storage Temperature: -65℃ to +150℃.

Features

Z85C3010VSC features: (1)Pin Compatible to NMOS Versions; (2)Two Independent, 0 to 4.1 Mbit/Second, Full-Duplex Channels. Each channel with Separate Crystal Oscillator, Baud Rate Gener­ator, and Digital Phase-Locked Loop (DPLL)for Clock Recovery; (3)Multi-Protocol Operation under Program Control; Programmable for NRZ, NRZI, or FM Data Encoding; (4)Asynchronous Mode with Five to Eight Bits and One, One and One-Half, or Two Stop Bits Per Character, Programmable Clock Factor, Break Detection and Generation; Parity, Overrun, and Framing Error Detection; (5)Synchronous Mode with Internal or External Character Synchroni­zation on One or Two Synchronous Characters and CRC Gener­ation and Checking with CRC-16 or CRC-CCITT Preset to either 1s or 0s; (6)SDLC/HDLC Mode with Comprehensive Frame-Level Control, Automatic Zero Insertion and Deletion, I-Field Residue Handling, Abort Generation and Detection, CRC Generation and Checking, and SDLC Loop; (7)Software Interrupt Acknowledge Feature (not available with NMOS); (8)Local Loopback and Auto Echo Modes; (9)Supports T1 Digital Trunk; (10)Enhanced DMA Support (not available with NMOS)10 x 19-Bit Status FIFO 14-Bit Byte Counter.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

Z85C3010VSC |

ZiLOG |

I/O Controller Interface IC 10 MHz Z8500 CMOS |

Data Sheet |

Negotiable |

|

||||

|

Z85C3010VSC00TR |

|

IC Z8500 SCC 44PLCC |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))